# Journal of Modeling & Simulation in Electrical & Electronics Engineering (MSEEE)

Journal homepage: https://mseee.semnan.ac.ir/

ISSN: 2821-0786

# Artificial Neural Networks and Hybrid Evolutionary Algorithms for Multi-Objective Optimization of Analog Integrated Circuit Design

Ali Bahadorinia1\*

Abstract-The design of analog integrated circuits demands the careful optimization of multiple interdependent parameters, including transistor sizes, bias currents, and passive components, to meet stringent performance targets such as gain, bandwidth, phase margin, and power efficiency. To address this challenge, this work introduces a computational intelligence framework that combines artificial neural networks (ANNs) with a hybrid genetic algorithm-particle swarm optimization (GA-PSO) strategy. The framework was validated on two representative circuits: a two-stage CMOS operational amplifier with Miller compensation and a differential LC voltage-controlled oscillator (LC-VCO) operating at 2.8 GHz in 0.18-µm CMOS technology. Extensive HSPICE simulations generated datasets that enabled the ANN to capture the complex nonlinear relationships between design variables performance metrics. The method successfully predicted optimal device dimensions and biasing conditions, achieving a 160% improvement in figure of merit (FoM) for the amplifier and a FoM of 118.1 dBc/Hz for the LC-VCO, comparable to state-of-the-art designs. These results demonstrate the framework's versatility and scalability, providing a flexible softcomputing tool for multi-objective optimization across diverse analog circuit topologies.

#### I. INTRODUCTION

Analog circuits play a crucial role in a wide range of applications, including wireless communications, biosensors, and numerous other fields [1–4].

Traditionally, the design parameters of analog circuits, such as transistor dimensions and biasing conditions, have been determined manually by designers based on experience and domain knowledge. This trial-and-error approach is not only time-consuming but also does not necessarily guarantee optimal designs. Moreover, due to the inherent trade-offs among circuit parameters, improving one performance metric can often lead to the degradation of another, making it challenging to satisfy stringent specifications. Consequently, with the growing demand for low-power, high-performance integrated circuits, adopting automated design methodologies has become increasingly important.

In recent years, artificial neural networks (ANNs) and evolutionary algorithms have emerged as powerful tools for optimizing analog circuit design [5-6]. Neural networks, owing to their parallel architecture, can perform high-speed computations that significantly reduce design time, while their adaptive nature allows them to be trained on inputoutput data and adjust to variations [7]. Simultaneously, advanced optimization techniques-including ant colony optimization [8–9], grey wolf optimization [10], genetic algorithms [11-12], differential evolution [13-14], and simulated annealing [15-16]—have been increasingly applied to determine optimal design parameters. Despite their advantages, these methods often face limitations such as slow convergence and a high risk of being trapped in local optima, preventing achieving globally optimal solutions. This work investigates the capability of a hybrid Genetic Algorithm-Particle Swarm Optimization (GA-PSO) framework in training neural networks to design analog circuits, generate

Received; 2025-09-08 Revised; 2025-09-27 Accepted; 2025-09-30

• Corresponding author Email: bahdorinia.a@gmail.com

#### Cite this article as:

Bahadorinia, A. (2025). Artificial Neural Networks and Hybrid Evolutionary Algorithms for Multi-Objective Optimization of Analog Integrated Circuit Design. *Journal of Modeling & Simulation in Electrical & Electronics Engineering (MSEEE)*, 5(2), 63-76.

DOI:https://doi.org/10.22075/MSEEE.2025.38966.1227

© 2025 The Author(s). Journal of Modeling & Simulation in Electrical & Electronics E published by Semnan University Press. This is an open access article under the CC-BY 4.0 license. (https://creativecommons.org/licenses/by/4.0/)

<sup>1.</sup> Department of Electrical Engineering, Faculty of Engineering, Hakim Sabzevari University, Sabzevar, Iran

novel designs, and enable user-defined trade-offs among parameters. design To demonstrate multiple generalization potential of the proposed framework, Validation Examples are provided, encompassing Validation Example I: Two-Stage CMOS Operational Amplifier and Validation Example II: Differential CMOS LC Voltage Controlled Oscillator (LC-VCO), illustrating its applicability across diverse analog circuit topologies. The remainder of the paper is organized as follows: Section 2 briefly reviews the application of neural networks in automated analog circuit design. Section 3 introduces the hybrid GA-PSO algorithm, while Section 4 details its use in neural network training. Section 5 presents validation examples of representative analog circuits. Section 6 discusses dataset generation via parallel HSPICE simulations, and Section 7 addresses data preprocessing for effective ANN training. Section 8 elaborates on neural network architecture selection and training, demonstrating the generation of new circuit designs and management of trade-offs among performance metrics. Finally, Section 9 provides a comparative analysis of the proposed methodology against existing approaches, highlighting its efficiency and versatility, followed by concluding remarks.

#### II. APPLICATION OF NEURAL NETWORKS IN AUTOMATED ANALOG CIRCUIT DESIGN

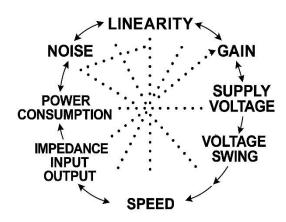

As previously outlined, the design of analog circuits—particularly operational amplifiers necessitates profound expertise to comprehend the intricate and nonlinear relationships that exist between design parameters and circuit performance metrics, alongside establishing optimal tradeoffs tailored to specific application requirements. As depicted in Fig. 1, variations in a single design parameter can exert direct or indirect effects on multiple performance characteristics, often in conflicting manners. For instance, an increase in supply voltage typically reduces input-referred noise, yet concurrently escalates the overall power consumption of the circuit.

Traditional intelligent analog design methodologies rely heavily on sophisticated physics-based formulations or detailed circuit-level simulations to model the complex interplay between design variables—such as transistor channel width and length—and key performance indicators including gain, power consumption, and gain—bandwidth product. However, to alleviate the complexity of these models, numerous physical and electronic phenomena are frequently omitted, which inevitably compromises the accuracy and reliability of the resultant designs.

In contrast, artificial neural networks (ANNs) offer a robust framework capable of addressing multivariate design challenges by directly mapping design inputs to performance outputs without explicit reliance on complex analytical equations. Moreover, once adequately trained, these neural models facilitate the generation of diverse circuit designs conforming to user-defined specifications. Consequently, the highly nonlinear and multidimensional characteristics inherent to analog circuit performance can be effectively encapsulated by training ANNs on sufficiently extensive and high-quality datasets.

Upon completion of training, the ANN can inversely infer optimal design parameters based on desired performance targets, thereby streamlining the analog design process [17].

Fig 1. Complicated and nonlinear relation of analog circuit performance parameters

### III. HYBRID GENETIC-PARTICLE SWARM OPTIMIZATION ALGORITHM (HGAPSO)

The Hybrid Genetic—Particle Swarm Optimization (HGAPSO) algorithm is developed by integrating the Genetic Algorithm (GA) with Particle Swarm Optimization (PSO). Given that both methods draw inspiration from natural phenomena, their foundational principles are first elaborated before introducing the hybridization approach.

#### A. Genetic Algorithm (GA)

The Genetic Algorithm (GA), originally proposed by John Holland in 1975 at the University of Michigan, is grounded in the principles of genetics and Darwinian evolution, fundamentally relying on the concept of "survival of the fittest" or natural selection. Among its prominent applications is its use as an optimization technique. GA has been extensively utilized in various fields such as pattern recognition, feature selection, image processing, and machine learning [18-19]. Conceptually, GA is a population-based stochastic search and optimization method inspired by natural genetic processes, aiming primarily to minimize a given cost or objective function. Unlike traditional optimization methods that initiate the search from a single solution, GA explores the search space starting from an entire population, thereby enhancing the probability of locating the global optimum. The operation of GA revolves around three core genetic operators:

- Selection

- Crossover

- Mutation

The selection operator is responsible for choosing individuals from the current population to form a new generation. This choice is predominantly influenced by the fitness value of each individual, where higher fitness correlates with a higher likelihood of selection. The probability  $P_i$  of selecting the  $i_{th}$  individual is computed as follows:

$$P_i = \frac{F_i}{\sum_{j=1}^{popsize} F_j} \tag{1}$$

Where  $F_i$  denotes the fitness value of the  $i_{th}$  individual and N is the population size. New generations are produced via the crossover and mutation operators, which are applied with

probabilities  $P_c$  and  $P_m$ , respectively. The iterative process continues until termination criteria are satisfied, such as reaching a predetermined maximum number of generations or achieving convergence indicated by a stable standard deviation in the population's fitness values.

#### B. Particle Swarm Optimization (PSO)

Particle Swarm Optimization (PSO) was first proposed by Kennedy and Eberhart in 1995 [20]. Similar to other population-based evolutionary algorithms, PSO initializes with a randomly generated population of candidate solutions, referred to as "particles." Each particle navigates the search space by iteratively updating its position based on its velocity, guided both by its individual best-known position (Pbest) and the global best position (Gbest) discovered by the swarm.

Consider a search space of dimension D, where the state of each particle is described by its position vector  $X_i$  and velocity vector  $V_i$ . The position and velocity of each particle at iteration t+1 are updated according to the following equations:

$$V_i^{t+1} = wV_i^t + C_1r_1(Pbest_i - X_i^t) + C_2r_2(gbest_i - X_i^t)$$

(2)

$$X_i^{t+1} = X_i^t + V_i^{t+1} (3)$$

Where  $V_i^{t+1}$  and  $V_i^t$  represent the updated and current velocity vectors of particle i, respectively;  $X_i^t$  and  $X_i^{t+1}$  denote the current and updated positions. The term Pbesti corresponds to the best position found individually by particle i, whereas Gbest signifies the best position identified by the entire swarm. The coefficients  $C_1$  and  $C_2$  are the cognitive and social acceleration factors, typically set within the range of 1 to 2. The stochastic variables  $r_1$  and  $r_2$  are uniformly sampled from the interval [0, 1]. The inertia weight w, usually assigned a value between 0.4 and 0.7, modulates the trade-off between global exploration and local exploitation.

### C. Hybrid Genetic-Particle Swarm Optimization Algorithm (HGAPSO)

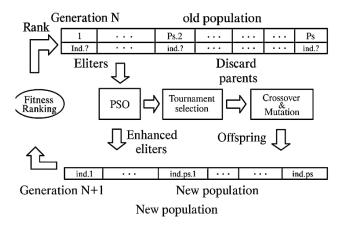

As previously discussed, the Particle Swarm Optimization (PSO) algorithm offers advantages such as rapid convergence and the ability to perform both global and local searches in parallel, maintaining an effective balance between exploration and exploitation. These characteristics can be leveraged to mitigate the issue of premature convergence typically observed in Genetic Algorithms (GA), thereby improving the quality of the selected parents. Consequently, the integration of GA and PSO forms a mutually complementary framework [21]. The HGAPSO algorithm operates based on this principle [22]. It starts with a randomly initialized population, and after evaluating the fitness of all individuals, the top 50% with the highest fitness scoresreferred to as elites—are selected. These elite individuals then undergo refinement using the PSO mechanism. The PSOdriven enhancement process improves the quality of the elites, producing higher-quality offspring in subsequent generations and enhancing the algorithm's exploratory capabilities.

In the final phase, the optimized elite individuals are directly transferred to the next generation, while the rest of the population is generated through traditional GA operations such as crossover and mutation. The overall workflow of the HGAPSO algorithm is depicted in Fig. 2.

Fig2. The implementation procedure of the HGAPSO algorithm

#### IV. NEURAL NETWORK TRAINING VIA THE HGAPSO ALGORITHM

In neural network training, the primary optimization parameters are the weights and biases associated with each neuron. If the *i*th layer of the network contains V input nodes and N neurons, the corresponding weight matrix  $W^i$  and bias vector  $B^i$  are defined as shown in (4):

$$W^{i} = \begin{bmatrix} (w_{1}^{i})^{t} \\ (w_{2}^{i})^{t} \\ \vdots \\ \vdots \\ (w_{n}^{i})^{t} \end{bmatrix} \qquad B^{i} = \begin{bmatrix} b_{1}^{i} \\ b_{2}^{i} \\ \vdots \\ \vdots \\ b_{n}^{i} \end{bmatrix}$$

$$(4)$$

In this study, the optimal values for these parameters are obtained using the HGAPSO algorithm. The procedure begins by initializing the weights and biases of all neurons with random values. The neural network is then executed using these initial values, and the resulting error from each forward pass is used as the fitness value to evaluate each candidate solution.

Subsequently, the HGAPSO algorithm updates the weights and biases based on its evolutionary equations. This iterative training process continues until either a predefined error threshold is met by one of the individuals or a stopping criterion (such as the maximum number of iterations) is reached. Upon completion of the training phase, the final optimized weights are used to compute the classification error on the training dataset. The same set of weights is then applied to evaluate the model's performance on the test dataset.

### V. VALIDATION EXAMPLES OF REPRESENTATIVE ANALOG CIRCUITS

# A. Validation Example I: Two-Stage CMOS Operational Amplifier

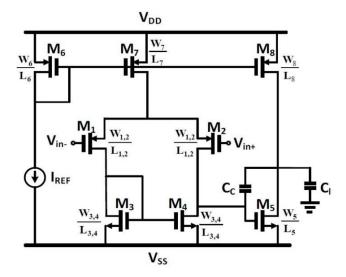

Validation Example I describes a two-stage CMOS operational amplifier incorporating a PMOS differential input pair along with Miller compensation, as shown in Fig. 3. In this design, the positive and negative supply voltages  $(V_{DD}$  and  $V_{SS})$  are set to +3.3 V and -3.3 V, respectively. Furthermore, the DC bias voltages applied to the differential

input terminals  $Vin_+$  and  $Vin_-$  are both maintained at 0.8 V, ensuring symmetric operation and stable amplifier performance.

Fig 3. Miller compensated two-stage operational amplifier

Furthermore, to prevent a mismatch in the differential pairs, the channel widths and lengths of transistors  $M_1$  and  $M_2$ , as well as  $M_3$  and  $M_4$ , are set to be identical. Accordingly, a sample design parameter vector  $V_i$  is defined as in (5):

$$V_i = \left[ W_{1,2}, W_{3,4}, W_5, W_6, W_7, W_8, L_{1,2}, L_{3,4}, L_5, L_6, L_7, L_8, I_{REF}, C_C, C_l \right]$$

(5)

Where W and L represent the channel width and length of the transistors, respectively.  $I_{REF}$  denotes the reference current source,  $C_C$  is the compensation capacitor, and  $C_l$  represents the load capacitor. Four key parameters are considered to evaluate the performance of the operational amplifier: low-frequency gain, power consumption, phase margin, and the gain—bandwidth product.

#### B. Validation Example II: Differential CMOS LC-VCO

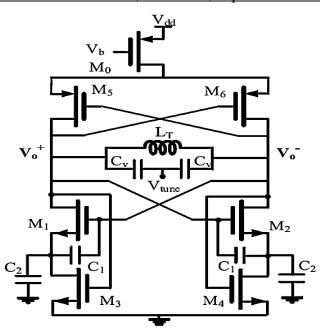

To further evaluate the generalization capability of the proposed ANN + GA-PSO framework, a second validation example was conducted on a differential CMOS LC voltagecontrolled oscillator (LC-VCO) operating at 2.76 GHz in a 0.18-µm CMOS technology. The oscillator is based on a Colpitts-inspired topology with capacitive feedback from the gate to the source, which provides high negative trans conductance and ensures reliable start-up even at low bias currents. To enhance negative trans conductance and achieve stable oscillation, the circuit incorporates cross-coupled PMOS transistors along with a differential LC tank. Key performance parameters, including negative trans conductance, oscillation frequency, and phase noise, were carefully analyzed and optimized [23]. The schematic of the designed LC-VCO is shown in Fig. 4.

Fig 4. The differential LC voltage-controlled oscillator (LC-VCO)

In this design, the output frequency is controlled via a tuning voltage  $V_{tune}$ , which is applied to accumulation-mode varactors. The applied tuning voltage modifies the varactors' capacitance, thereby adjusting the oscillator's frequency. These varactors enable precise frequency control, making the LC-VCO highly tunable and suitable for high-performance analog applications. Based on this, a sample design parameter vector  $V_i$  is defined as shown in (6):

$$V_i = \left[ W/L_{1,2}, W/L_{3,4}, W/L_{5,6}, L_T, C_V, C_1, C_2 \right]$$

(6)

### VI. DATA ACQUISITION FROM ANALOG CIRCUIT PERFORMANCE

One of the major challenges in leveraging artificial neural networks for automated analog circuit design lies in obtaining a representative and high-quality dataset from the complex performance landscape of analog circuits, which is essential for effective neural model training. Previous studies have employed various strategies for dataset generation, including intelligent and adaptive sampling within the design space [24–29], extracting data from ongoing optimization algorithm executions [30], and selecting feasible initial points followed by parameter variation in their vicinity [31].

In this work, a two-step sampling approach is adopted. First, a global random search is conducted to identify initial points across the entire design space, followed by localized sampling around these points through small perturbations to enhance sampling density and reduce computational overhead. The design space boundaries defined by the minimum and maximum allowable values of critical design parameters, such as transistor dimensions and reference current sources, are set based on technological and design constraints, as detailed in Table I.

For the initial global search, 1000 random design points are generated per iteration within the specified parameter ranges. This process yields a 15×1000 matrix, where each row corresponds to a distinct set of 15 design parameters. Each candidate design is then simulated using HSPICE on the twostage operational amplifier model depicted in Fig. 3. All circuit simulations were conducted using HSPICE version 2021.09, under the typical-typical (TT) process corner, and at a nominal temperature of 25 °C. Four key performance metrics are extracted for each design point: low-frequency gain, power consumption, phase margin, and gain-bandwidth product. Next, acceptable ranges for average performance metrics are defined (see Table II), and design points outside these thresholds are discarded to focus on regions with moderate yet meaningful performance levels, thereby accelerating dataset collection. This phase continues until 100 acceptable initial points are identified. Subsequently, the design parameters around each point are iteratively varied by up to 30%, and any newly generated acceptable points are added to the reference set for further neighborhood exploration. This iterative refinement continues until 8000 valid design points are collected.

To ensure a balanced representation of the design space, we employed a two-step sampling approach, followed by a dedicated evaluation of potential dataset bias. While the initial sampling focused on points within acceptable performance ranges to accelerate data collection, supplementary experiments were conducted in which a subset of low-performance points was deliberately included. This allowed the ANN to capture broader design relationships, and the results confirmed that the network's predictions remain stable and robust, demonstrating effective generalization across the design space.

Finally, an outlier removal step is performed, whereby any design point exhibiting deviations exceeding three standard deviations from the global mean (computed over all 8,000 samples) in any of the key performance metrics is excluded. This filtering reduces dataset variance and improves the quality and robustness of neural network training. In this study, parallel processing was employed in HSPICE to accelerate sampling and reduce the overall design process time. The computations were carried out on a workstation with 16 GB of RAM and a quad-core Intel processor operating at a maximum clock speed of 2.4 GHz, which reduced the total sampling time for data collection to 37 minutes and 43 seconds.

TABLE I

Design Parameters and their Acceptable Ranges

| Besign rarameters and their receptuate ranges |                     |                  |                         |           |         |  |  |  |  |

|-----------------------------------------------|---------------------|------------------|-------------------------|-----------|---------|--|--|--|--|

| Design<br>Parameter                           | Minimu<br>m<br>(µm) | Maximu<br>m (μm) | Design<br>Param<br>eter | Minimum   | Maximum |  |  |  |  |

| $W_{1,2}$                                     | 0.18                | 200              | $W_7$                   | 0.18 (µm  | 200(µm) |  |  |  |  |

| $L_{1,2}$                                     | 0.18                | 3                | L <sub>7</sub>          | 0.18(µm)  | 3(µm)   |  |  |  |  |

| $W_{3,4}$                                     | 0.18                | 200              | $W_8$                   | 0.18(µm)  | 200(µm) |  |  |  |  |

| L <sub>3,4</sub>                              | 0.18                | 3                | <i>L</i> <sub>8</sub>   | 0.18(µm)  | 13(µm)  |  |  |  |  |

| $W_5$                                         | 0.18                | 200              | I <sub>REF</sub>        | 0.1 (µA)  | 120(µA) |  |  |  |  |

| <i>L</i> <sub>5</sub>                         | 0.18                | 3                | $C_l$                   | 0.001(pF) | 10 (pF) |  |  |  |  |

| W <sub>6</sub>                                | 0.18                | 200              | Cc                      | 0.001(pF) | 10 (pF) |  |  |  |  |

| <i>L</i> <sub>6</sub>                         | 0.18                | 3                |                         |           |         |  |  |  |  |

TABLE II

Performance Parameters and their Acceptable Ranges for

Training Dataset

| Performance Parameter           | Minimum  | Maximum |  |  |

|---------------------------------|----------|---------|--|--|

| Low-frequency gain              | 40 dB    | 60 dB   |  |  |

| Power consumption               | 0.1 mW   | 10 mW   |  |  |

| Phase margin                    | 55       | 100     |  |  |

| Gain-bandwidth product<br>(GBW) | 0.01 MHz | 10 MHz  |  |  |

Similarly, the same procedure was used to acquire data from the LC-VCO, generating 1000 random design points per iteration within the predefined parameter ranges. This produced a 7×1000 matrix, each row representing a unique combination of seven key design parameters. Four main performance metrics—oscillation frequency, power consumption, phase noise, and the figure of merit (FOM), detailed in Section 9—were carefully evaluated to facilitate meaningful comparisons with recent designs.

#### VII. DATA NORMALIZATION

Following the extraction of input and output datasets from HSPICE simulations, the subsequent step in the modeling pipeline involves data normalization to standardize the dataset for effective neural network training. Given the considerable disparity in the scales of design variables and performance metrics—for example, transistor widths measured in micrometers versus DC gain expressed in decibels—normalization is imperative to mitigate scale-induced bias and facilitate the convergence of the training algorithm. In this work, a min-max normalization technique is applied to rescale all variables within the interval [0, 1], as formalized in (7):

$$x_{norm} = \frac{x - x_{min}}{x_{max} - x_{min}} \tag{7}$$

Where x denotes the original data value and  $x_{norm}$  represents the normalized output.

## VIII. STRUCTURE OF THE ARTIFICIAL NEURAL NETWORK AND TRAINING PROCEDURE

In the present work, a feed-forward multilayer perceptron (MLP) comprising two hidden layers is employed to model the performance characteristics of the operational amplifier under investigation. The neural network is developed using MATLAB's Neural Network Toolbox. The input layer consists of 15 neurons, each corresponding to specific design parameters including the transistor width-to-length (W/L) ratios, bias current, and values of compensation and load capacitors. The architecture features two hidden layers: the first with 10 neurons and the second with 7 neurons, both utilizing the sigmoid activation function to introduce nonlinearity. The output layer comprises four neurons, each representing a key circuit performance metric: low-frequency gain, unity-gain bandwidth (GBW), power consumption, and phase margin. A linear activation function is adopted in the output layer to facilitate accurate prediction of continuous output values. Training is conducted using a hybrid optimization algorithm that integrates Genetic Algorithm (GA) and Particle Swarm Optimization (PSO). During the initial training phases, GA's extensive global search capabilities guide exploration of the solution space, while in the final stages, PSO's rapid convergence is leveraged to refine and optimize the model parameters. To mitigate overfitting, the dataset is partitioned into training and testing subsets, allocating 80% of the data for training and the remaining 20% for validation. The optimization objective is to minimize the mean squared error (MSE) between the predicted outputs and the corresponding ground truth values.

#### IX. DESIGN RESULTS AND PERFORMANCE ANALYSIS

The training was carried out on a workstation equipped with 16 GB of RAM and a quad-core Intel processor operating at a maximum clock speed of 2.4 GHz, requiring approximately two minutes to complete.

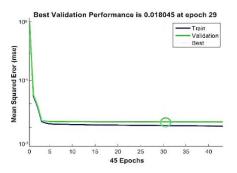

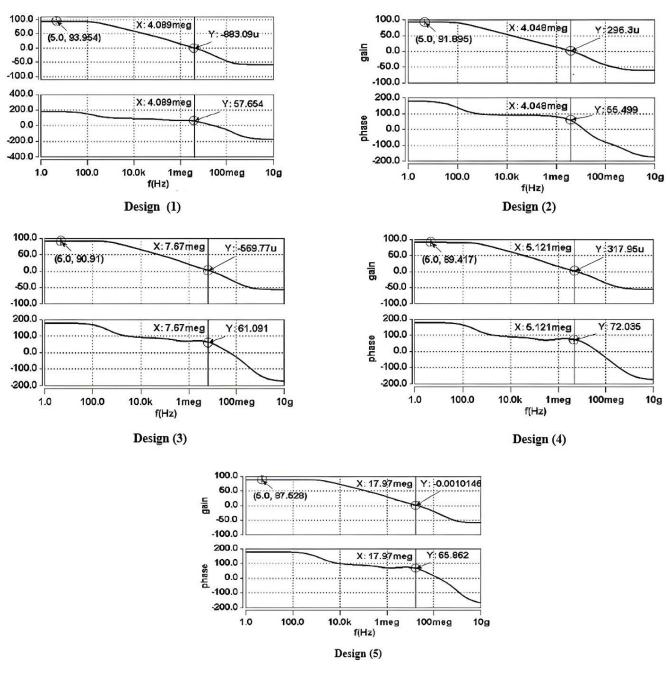

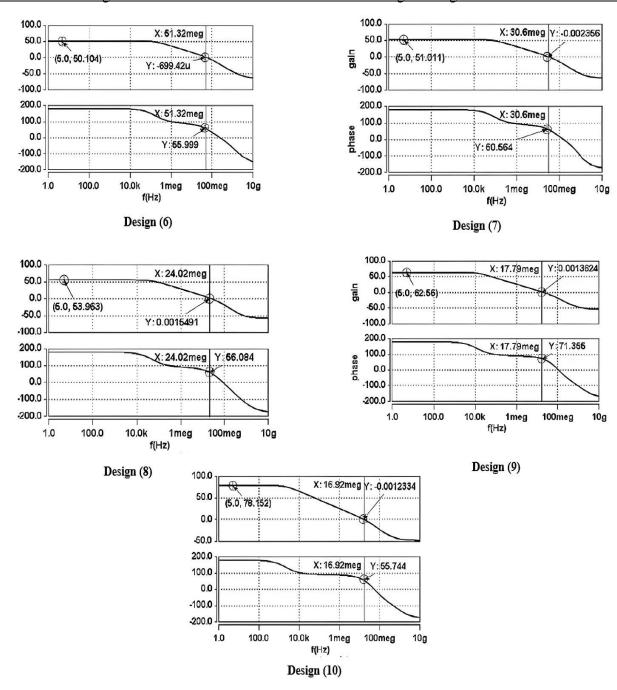

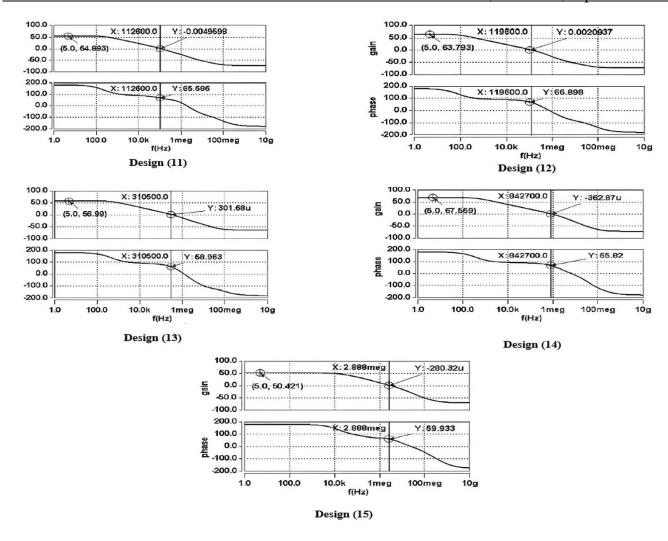

The training outcomes are depicted in Fig. 5. The final mean squared errors (MSE) for the training and validation datasets were 0.01012 and 0.01804, respectively. Following the completion of the neural network training, the model was employed to generate novel circuit designs. From these, the fifteen top-performing configurations, each optimized for different performance criteria, were selected and summarized in Table III. These configurations are classified into three principal categories based on their optimization objectives: maximization of the DC gain, maximization of the gain-bandwidth product (FoM), and minimization of power consumption. A concise analysis of the salient features for each category is provided in the subsequent subsections.

It should be emphasized that a widely recognized figure of merit, commonly employed in recent and reputable studies for assessing the performance of operational amplifiers [32-35], was computed for each configuration in accordance with (8).

$$FOM = \frac{GBW \times C_{Load}}{p} \tag{8}$$

Also, to evaluate the figure of merit (FOM) of the VCO, this study adopts the standard formulation widely employed in recent oscillator design literature [42-48], as expressed in (9).

$$FoM = L(\nabla \omega) + 10Log P_{DC} - 20Log \left(\frac{\omega_0}{\nabla \omega}\right)$$

(9)

Fig 5. Train and validation error during training

In this formulation,  $L(\nabla \omega)$  represents the single-sideband phase noise measured at an offset frequency of  $\nabla \omega$  while  $\omega_0$  denotes the oscillation frequency. The term  $P_{DC}$  corresponds to the circuit's power consumption, expressed in mW. Moreover, FTR indicates the frequency tuning range, and  $\Delta V_{tune}$  specifies the span of the tuning voltage variation.

TABLE III

Performance of Sampled Designs from the Trained ANN

| Deign Objective                  | Low-<br>Frequency<br>Gain (dB) | Gain–Bandwidth<br>Product (FoM)<br>MHz | Power<br>Consumption<br>(mW) | Phase Margin (°) |

|----------------------------------|--------------------------------|----------------------------------------|------------------------------|------------------|

| Objective 1 – Maximum<br>DC Gain | > 85                           | > 4.0                                  | < 1.0                        | Range: 55–100    |

| Design 1                         | 94.225                         | 4.097                                  | 0.05048                      | 58.358           |

| Design 2                         | 92.769                         | 4.036                                  | 0.2704                       | 56.351           |

| Design 3                         | 91.85                          | 7.34                                   | 0.04575                      | 60.254           |

| Design 4                         | 90.953                         | 5.632                                  | 0.1123                       | 73.260           |

| Design 5                         | 89.417                         | 18.01                                  | 0.4152                       | 67.523           |

| Objective 2 – Maximum            |                                |                                        |                              |                  |

| Gain-Bandwidth Product           | > 50                           | > 12.0                                 | < 1.0                        | Range: 55-100    |

| (FoM)                            |                                |                                        |                              |                  |

| Design 6                         | 52.417                         | 52.15                                  | 0.764                        | 56.346           |

| Design 7                         | 53.635                         | 32.65                                  | 0.9845                       | 61.523           |

| Design 8                         | 55.856                         | 26.78                                  | 0.4568                       | 57.369           |

| Design 9                         | 63.658                         | 19.97                                  | 0.7348                       | 72.663           |

| Design 10                        | 79.512                         | 18.25                                  | 0.6856                       | 57.256           |

| Objective 3 – Minimum            |                                |                                        |                              |                  |

| <b>Power Consumption</b>         | > 50                           | > 0.1                                  | < 0.1                        | Range: 55-100    |

| Design 11                        | 56.365                         | 0.1231                                 | 0.002359                     | 67.236           |

| Design 12                        | 65.472                         | 0.1298                                 | 0.003847                     | 68.545           |

| Design 13                        | 58.765                         | 0.4967                                 | 0.008153                     | 61.453           |

| Design 14                        | 69.538                         | 0.9573                                 | 0.01014                      | 69.547           |

| Design 15                        | 52.142                         | 3.745                                  | 0.02878                      | 62.987           |

The initial five designs were developed with the primary objective of maximizing DC gain while ensuring low power consumption and maintaining sufficient stability, characterized by a high phase margin. Within this subset, Design 1 exhibits the superior overall performance, achieving a gain of 94.225 dB, a power dissipation of merely 0.05048 mW, and a phase margin of 58.36°. Designs 6 through 10 were synthesized to optimize the gain-bandwidth product (Av×GBW). Among these, Design 6 attained the highest figure of merit (FoM) of 52.15. The final cluster, encompassing Designs 11 to 15, curated to prioritize power consumption minimization. Notably, Design 11 distinguishes itself as one of the most energy-efficient architectures, with a power consumption of only 0.002359 mW, while sustaining acceptable performance metrics such as a gain of 56.365 dB and a phase margin of 67.236°.

The data summarized in Table III substantiate that the neural network model, once trained, can generate a broad

spectrum of optimized designs tailored to distinct performance criteria. These designs effectively balance high gain, low power usage, and satisfactory stability, thereby validating the accuracy and practical applicability of the proposed model within the inverse design framework of analog circuits. Corresponding design parameters derived from the neural network predictionscovering transistor channel dimensions, reference current source, compensation capacitance, and load capacitance for maximum low-frequency gain, maximum gainbandwidth product, and minimum power consumption are detailed in Tables IV, V, and VI, respectively. Furthermore, the frequency response of each group of these designs is presented in Fig.s 6, 7, and 8, respectively. Drawing inspiration from dynamic high fan-in OR gate designs, the proposed neural-network-assisted operational amplifier demonstrates a notable reduction in power consumption while effectively maintaining all critical performance metrics [1].

TABLE IV

The Corresponding Design Parameters of the ANN Predicted Designs to Reach the Best DC Gain.

|          | $W_{1,2}$ | $W_{3,4}$ | $W_5$  | $W_6$  | $W_7$          | $W_8$  | I <sub>REF</sub> | $C_c$  | $c_l$ |

|----------|-----------|-----------|--------|--------|----------------|--------|------------------|--------|-------|

|          | $L_{1,2}$ | $L_{3,4}$ | $L_5$  | $L_6$  | L <sub>7</sub> | $L_8$  | (μA)             | (pF)   | (pF)  |

| Design 1 | 17.45     | 24.26     | 27.63  | 11.23  | 0.9852         | 6.745  | 14.52            | 0.1813 | 2.756 |

|          | 7.536     | 22.15     | 0.3236 | 14.19  | 9.2141         | 13.563 |                  |        |       |

| Design 2 | 28.46     | 12.56     | 26.41  | 2.03   | 25.32          | 14.55  | 53.12            | 2.023  | 6.402 |

|          | 6.423     | 5.326     | 2.231  | 2.043  | 25.63          | 22.65  |                  |        |       |

| Design 3 | 18.42     | 25.36     | 29.47  | 11.54  | 8.652          | 29.45  | 7.521            | 0.0857 | 1.756 |

|          | 11.76     | 19.52     | 0.2941 | 10.362 | 25.32          | 14.32  |                  |        |       |

| Design 4 | 22.35     | 26.23     | 11.74  | 19.44  | 5.771          | 27.45  | 21.632           | 0.1128 | 2.145 |

|          | 21.54     | 30.32     | 0.3145 | 9.525  | 29.47          | 13.88  |                  |        |       |

| Design 5 | 104.56    | 30.56     | 22.74  | 3.231  | 18.54          | 18.441 | 5.23             | 0.2223 | 3.475 |

|          | 5.326     | 24.68     | 0.5123 | 24.15  | 22.56          | 8.023  |                  |        |       |

$TABLE\ V$  Corresponding Design Parameters of the ANN Predicted Designs to Reach the Best Gain-Bandwidth Product.

|           | $W_{1,2}$ | W <sub>3,4</sub> | $W_5$  | $W_6$  | $W_7$  | W <sub>8</sub> | I <sub>REF</sub> | (pF)   | $c_l$ |

|-----------|-----------|------------------|--------|--------|--------|----------------|------------------|--------|-------|

|           | $L_{1,2}$ | $L_{3,4}$        | $L_5$  | $L_6$  | $L_7$  | $L_8$          | $L_8$ $(\mu A)$  |        | (pF)  |

| Design 6  | 40.53     | 87.65            | 9.235  | 103.15 | 199.41 | 5.214          | 78.15            | 0.0241 | 8.471 |

|           | 0.5026    | 0.2317           | 0.355  | 3.078  | 2.151  | 0.8626         |                  |        |       |

| Design 7  | 22.54     | 15.26            | 77.25  | 7.235  | 103.4  | 96.24          | 34.15            | 0.7145 | 9.478 |

|           | 0.5031    | 0.3052           | 0.2236 | 2.066  | 3.882  | 3.141          |                  |        |       |

| Design 8  | 47.96     | 37.21            | 84.32  | 68.02  | 99.12  | 8.512          | 17.21            | 0.6814 | 5.236 |

|           | 0.5523    | 0.3625           | 0.2352 | 2.145  | 3.750  | 0.207          |                  |        |       |

| Design 9  | 39.45     | 32.33            | 72.78  | 13.56  | 81.54  | 48.56          | 36.5             | 1.547  | 4.214 |

|           | 2.231     | 1.238            | 0.3236 | 0.4758 | 3.142  | 0.702          |                  |        |       |

| Design 10 | 122.45    | 76.35            | 199.32 | 119.5  | 96.47  | 165.21         | 72.15            | 2.845  | 5.745 |

|           | 2.475     | 1.215            | 0.4452 | 2.452  | 2.452  | 1.315          |                  |        |       |

Fig 6. The gain and phase frequency response plots of the predicted designs to reach the best DC gain

TABLE VI Corresponding Design Parameters of the ANN Predicted Designs to Reach the Best Power Dissipation.

| Corres | Corresponding Design Farameters of the Arriv Tredicted Designs to Reach the Best Fower Dissipation. |           |        |        |                |        |                  |         |                 |  |  |

|--------|-----------------------------------------------------------------------------------------------------|-----------|--------|--------|----------------|--------|------------------|---------|-----------------|--|--|

|        | $W_{1,2}$                                                                                           | $W_{3,4}$ | $W_5$  | $W_6$  | $W_7$          | $W_8$  | I <sub>REF</sub> | $C_c$   | $C_l$           |  |  |

|        | $L_{1,2}$                                                                                           | $L_{3,4}$ | $L_5$  | $L_6$  | L <sub>7</sub> | $L_8$  | $(\mu A)$        | (pF)    | $(\mathbf{pF})$ |  |  |

| Design | 7.452                                                                                               | 17.23     | 30.35  | 28.36  | 16.78          | 28.152 | 0.5165           | 0.5882  | 6.178           |  |  |

| 11     | 9.025                                                                                               | 26.74     | 0.3625 | 14.36  | 21.26          | 11.25  |                  |         |                 |  |  |

| Design | 9.989                                                                                               | 16.84     | 15.89  | 6.36   | 8.452          | 19.563 | 0.5158           | 1.758   | 8.541           |  |  |

| 12     | 16.53                                                                                               | 14.25     | 0.6958 | 9.153  | 28.51          | 10.26  |                  |         |                 |  |  |

| Design | 30.26                                                                                               | 11.81     | 29.52  | 4.266  | 11.53          | 19.25  | 1.125            | 2.536   | 8.658           |  |  |

| 13     | 14.362                                                                                              | 2.365     | 0.5685 | 6.256  | 26.14          | 3.845  |                  |         |                 |  |  |

| Design | 66.23                                                                                               | 37.23     | 1.097  | 76.521 | 93.45          | 3.891  | 1.741            | 0.00974 | 9.698           |  |  |

| 14     | 0.9863                                                                                              | 0.652     | 0.4544 | 2.712  | 2.142          | 3.462  |                  |         |                 |  |  |

| Design | 22.45                                                                                               | 17.25     | 7.032  | 9.256  | 4.896          | 25.14  | 2.475            | 0.02941 | 9.075           |  |  |

| 15     | 27.65                                                                                               | 25.33     | 0.1599 | 30.48  | 13.48          | 29.41  |                  |         |                 |  |  |

Fig7. The gain and phase frequency response plots of the predicted designs for reaching the best gain-bandwidth product

$\label{eq:table_vii} \textbf{TABLE VII}$  Optimized LC-VCO Design Parameters Obtained Using the ANN + GA-PSO Framework

| Component             | Parameter / Value                 |

|-----------------------|-----------------------------------|

| Transistors           |                                   |

| M <sub>1-2</sub>      | $W/L = 50 / 0.18 \ \mu m / \mu m$ |

| M <sub>3-4</sub>      | $W/L = 22 / 0.18 \ \mu m / \mu m$ |

| M <sub>5-6</sub>      | $W/L = 150 / 0.18  \mu m / \mu m$ |

| Inductor & Capacitors |                                   |

| $L_T$                 | 3.25 nH                           |

| $C_v$                 | 184 fF                            |

| $C_1$                 | 1.5 pF                            |

| $C_2$                 | 3 pF                              |

Fig 8. The gain and phase frequency response plots of the predicted designs to reach the best power dissipation

As previously mentioned, to further evaluate the generalization capability of the proposed ANN + GA–PSO framework, a second case study was conducted on a differential CMOS LC voltage-controlled oscillator (LC-VCO) operating at 2.76 GHz in 0.18- $\mu m$  CMOS technology. The design and simulation of the circuit were carried out using the same ANN + GA–PSO methodology employed in the first case study.

In the LC-VCO design, the key circuit parameters considered as decision variables included the tank capacitors (C1 and C2), transistor dimensions, and voltages. To achieve multi-objective performance optimization, various combinations of these parameters were simulated to obtain the output characteristics of each configuration, including oscillation frequency, power consumption, phase noise, and negative trans conductance. These outputs served as training data for the artificial neural network, allowing the algorithm to determine the optimal parameter combination that ensures reliable startup, low phase noise, and minimal power consumption. In other words, each simulation constituted a training

sample for the neural network, enabling it to learn the relationships between circuit parameters and the VCO's final performance, and to propose an optimized configuration. The design parameters of the LC-VCO optimized using the ANN+GA-PSO framework are summarized in Table VII .

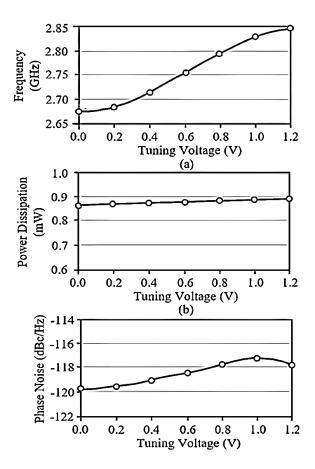

As  $V_{tune}$  varies from 0 to 1.2 V, the LC-VCO exhibits an oscillation frequency range of 2.68–2.85 GHz. Simulation results demonstrate that, under a 1.4 V supply, the oscillator achieves a frequency of 2.83 GHz, with a power consumption of 864  $\mu$ W and a phase noise of approximately –118.1 dBc/Hz at a 1 MHz offset. These findings confirm reliable startup, low power consumption, and minimal phase noise, highlighting the capability of the proposed framework to optimize complex analog circuits beyond conventional operational amplifiers. For a more detailed evaluation, the dependencies of oscillation frequency, power consumption, and phase noise on varying control voltages are depicted in Fig. 9.

TABLE VIII

Comparison of Two-Stage Operational Amplifier Design Results with Other Methods

| Reference | Amplifier<br>Topology                                    | Technology (μm) | Design<br>Method                            | Gain–<br>Bandwidth<br>Product<br>(MHz) | Power<br>Consumpti<br>on (mW) | Load<br>Capacitance<br>(pF) | Figure of<br>Merit<br>(MHz·pF/mW) |

|-----------|----------------------------------------------------------|-----------------|---------------------------------------------|----------------------------------------|-------------------------------|-----------------------------|-----------------------------------|

| [36]      | Two-stage<br>with Miller<br>compensati<br>on             | 0.18            | Evolutionar<br>y<br>Algorithm<br>(MCO)      | 251                                    | 4.2                           | 1                           | 59.761                            |

| [37]      | Two-stage with Miller compensati on and nulling resistor | 0.13            | Swarm Intelligence -based Algorithm (CRPSO) | 111.2                                  | 0.01961                       | 0.05                        | 283.528                           |

| [38]      | Two-stage<br>with Miller<br>compensati<br>on             | 0.35            | Hybrid<br>Algorithm<br>(RPSODE)             | 5.526                                  | 0.8794                        | 10                          | 62.838                            |

| [39]      | Two-stage<br>with Miller<br>compensati<br>on             | 0.13            | Metaheurist<br>ic<br>Algorithm<br>(WOA)     | 4.293                                  | 0.266                         | 7                           | 112.973                           |

| [40]      | Two-stage<br>with Miller<br>compensati<br>on             | 0.35            | Evolutionar<br>y<br>Algorithm<br>(GA)       | 0.1037                                 | 0.0202                        | 0.05                        | 0.256                             |

| [40]      | Two-stage<br>with Miller<br>compensati<br>on             | 0.35            | Swarm Intelligence -based Algorithm (ACO)   | 0.1                                    | 0.01975                       | 0.05                        | 0.253                             |

| [41]      | Two-stage<br>with Miller<br>compensati<br>on             | 0.18            | Metaheurist<br>ic<br>Algorithm<br>(GWO)     | 8.63                                   | 1.6                           | 12                          | 64.725                            |

| This work | Two-stage<br>with Miller<br>compensati<br>on             | 0.18            | ANN +<br>GA-PSO<br>(Proposed<br>Method)     | 7.34                                   | 0.04575                       | 0.0857                      | 735.23                            |

TABLE IX

Performance Summary of the Proposed Voltage-Controlled Oscillator (VCO) and some other VCOs

| Reference | Tech.<br>(nm) | F <sub>OSC</sub><br>(GHz) | V <sub>DD</sub> (V) | P <sub>dis</sub> (mW) | <i>TR</i> (%) | PN @1<br>MHz<br>(dBc/Hz) | FoM     |

|-----------|---------------|---------------------------|---------------------|-----------------------|---------------|--------------------------|---------|

| [42]      | 180           | 30                        | 1.8                 | 27.4                  | 10.4          | 106.8                    | -179    |

| [43]      | 180           | 4                         | 1.8                 | 1                     | NA            | -116.8                   | -188.9  |

| [44]      | 65            | 24                        | 1.2                 | 12.8                  | 29            | -106                     | -185    |

| [45]      | 90            | 2.6                       | 1                   | 1.875                 | NA            | -120.97                  | -186.54 |

| [46]      | 130           | 2.4                       | 1                   | 0.262                 | 10            | -114.7                   | -188.15 |

| [47]      | 180           | 1.7                       | 1.8                 | 37.2                  | 82.4          | -110                     | 158.54  |

| [48]      | 90            | 1.77                      | 1.2                 | 3.96                  | 6.2           | -112                     | -171    |

| This work | 180           | 2.83                      | 1.4                 | 0.864                 | 6.3           | -118.1                   | -187.5  |

Fig. 9. (a) Output oscillation frequency, (b) power dissipation, and (c) PN of the proposed voltage-controlled oscillator (VCO) for different tuning voltages (Vtune). PN, phase noise.

Furthermore, a comparative overview of the designed VCO using the ANN+HGAPSO hybrid methodology relative to other designs reported in the literature is presented in Table IX.

### X. COMPARISON WITH PREVIOUS STUDIES AND CONCLUSION

In this study, we introduced a systematic computational intelligence framework for the design and multi-objective optimization of analog integrated circuits, initially validated on a two-stage operational amplifier. The framework synergistically combines Artificial Neural Networks (ANNs) with a hybrid metaheuristic algorithm integrating Genetic Algorithm (GA) and Particle Swarm Optimization (PSO), enabling accurate modeling of the complex relationships between critical design parameters and circuit performance while efficiently navigating the high-dimensional design space. The optimization focused on three primary objectives: maximizing low-frequency gain, improving the gainbandwidth product, and minimizing power consumption. Among the optimized solutions, the design targeting the gain-bandwidth product (Design 3) achieved a wellbalanced trade-off, delivering a gain-bandwidth product of 7.34 MHz, power consumption of 0.046 mW, and a load capacitance of 0.086 pF. Comparative analysis revealed a notable enhancement in the figure of merit (FoM), rising from 283 MHz•pF/mW in previous studies to 735 MHz•pF/mW, representing an approximate improvement.

To further evaluate the generalizability of the proposed approach, the methodology was applied to a differential LC voltage-controlled oscillator (LC-VCO) operating at 2.8 GHz in 0.18-µm CMOS technology. Extensive HSPICE simulations generated comprehensive datasets, enabling the ANN to capture intricate nonlinear dependencies between design variables and performance metrics. The framework successfully predicted optimal device dimensions and biasing conditions, achieving a FoM of 118.1 dBc/Hz for the LC-VCO, comparable to state-of-the-art designs. Overall, the results highlight the robustness, efficiency, and versatility of the ANN-assisted hybrid methodology. This work demonstrates that integrating ANN modeling with hybrid metaheuristic optimization provides a reliable and generalizable strategy for achieving optimal trade-offs in high-performance analog circuits. While the framework is inherently versatile, the current validation primarily relies on the two-stage op-amp and the additional LC-VCO case study. It is also important to acknowledge that additional factors, such as chip area, mismatch effects, process variations, and temperature dependence, play a critical role in analog IC design and can significantly influence the final performance. These aspects are recommended as key directions for future research to further enhance the applicability and comprehensiveness of the proposed framework.

#### REFERENCES

- [1] M. Asyaei, "Energy-Efficient Dynamic Circuit for High Fan-In OR Gates," *Modeling and Simulation in Electrical & Electronics Engineering (MSEEE)* 7 (2019) 23–34. https://doi.org/10.1001/1.23223871

- [2] N. Rahimzadeh, "Wideband Balun-LNA Employing gm-Boosting Feedback and Modified Current Bleeding Circuit," *Modeling and Simulation in Electrical & Electronics Engineering (MSEEE)* 8 (2020) 45–56. https://doi.org/10.1001/1.23223871

- [3] B. Rostami, F. Shanehsazzadeh, and M. Fardmanesh, "Fast Fourier transform based NDT approach for depth detection of hidden defects using HTS rf-SQUID," *IEEE Trans. Appl. Supercond.* 28 (2018) 1–6. https://doi.org/10.1109/TASC.2018.2841927

- [4] B.J. Hosticka, W. Brockherde, D. Hammerschmidt, and R. Kokozinski, "Low-voltage CMOS analog circuits," *IEEE Trans. Circuits Syst. I: Fundam. Theory Appl.* 42 (1995) 864–872. https://doi.org/10.1109/81.477197

- [5] S.P. Mohanty and E. Kougianos, "Biosensors: A tutorial review," IEEE Potentials 25 (2006) 35–40. https://doi.org/10.1109/MP.2006.1649009

- [6] S.M.A. Zanjani, M. Aalipour, and M. Parvizi, "Design of a low power temperature sensor based on sub-threshold performance of carbon nanotube transistors with an inaccuracy of 1.5°C for the range of -30 to 125°C," *J. Intell. Process. Electr. Technol.* 13 (2022) 115–127. https://doi.org/10.1001.1.23223871.1401.13.50.7.8

- [7] M. Barros, J. Guilherme, and N. Horta, "Analog circuits optimization based on evolutionary computation techniques," *Integration* 43 (2010) 136–155.

- [8] A. Jafarri, S. Sadri, and M. Zekri, "Design optimization of analog integrated circuits by using artificial neural networks," in: *Proc. Int. Conf. Soft Comput. Pattern Recognit. (SOCPAR)* (2010) 385–388.

- [9] K. Chau and C. Cheng, "Real-time prediction of water stage with artificial neural network approach," *Lect. Notes Artif. Intell.* 2557 (2002) 715

- [10] O. Bouattane and B. Benhala, "GA and ACO techniques for the analog circuits design optimization," *J. Theor. Appl. Inf. Technol.* 64 (2014) 413–419.

- [11] B. Benhala, A. Ahaitouf, A. Mechaqrane, B. Benlahbib, F. Abdi, E.H. Abarkan, and M. Fakhfakh, "Sizing of current conveyors by means of an ant colony optimization technique," in: *Proc. IEEE Int. Conf. Multimedia Comput. Syst. (ICMCS)*, Ouarzazate, Morocco (2011) 1–6. https://doi.org/10.1109/ICMCS.2011.5945669

- [12] E.M. Abdelkader, A. Al-Sakkaf, N. Elshaboury, and G. Alfalah, "Hybrid grey wolf optimization-based Gaussian process regression model for simulating deterioration behavior of highway tunnel components," *Processes* 10 (2022) 36. https://doi.org/10.3390/pr10010036

- [13] Y. Jiang, J. Ju, X. Zhang, and B. Yang, "Automated analog circuit design using Genetic Algorithms," in: *Proc. IEEE Int. Conf. ASIC Design (ICASID)*, Hong Kong (2009) 223–228. https://doi.org/10.1109/icasid.2009.5276912

- [14] J.B. Grimbleby, "Automatic analogue circuit synthesis using genetic algorithms," *IEE Proc. Circuits Devices Syst.* 147 (2001) 319–323. https://doi.org/10.1049/ip-cds:20000770

- [15] B. Liu, F.V. Fernandez, and G.G.E. Gielen, "Efficient and accurate statistical analog yield optimization and variation-aware circuit sizing based on computational intelligence techniques," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.* 30 (2011) 793–805. https://doi.org/10.1109/TCAD.2011.2106850

- [16] H. Yuan and J. He, "Evolutionary design of operational amplifier using variable-length differential evolution algorithm," in: *Proc. IEEE Int. Conf. Circuits, Syst., Modeling Simulation (ICCASM)*, Taiyuan, China (2010) 610–614. https://doi.org/10.1109/icca-sm.2010.5620307

- [17] R.A. Rutenbar, "Simulated annealing algorithms: An overview," *IEEE Circuits Devices Mag.* 5 (1989) 19–26. https://doi.org/10.1109/101.17235

- [18] S. Kirkpatrick, C.D. Gelatt, and M.P. Vecchi, "Optimization by simulated annealing," *Science* 220 (1983) 671–680. https://doi.org/10.1126/science.220.4598.671

- [19] N. Lourenço, E. Afacan, R. Martins, F. Passos, A. Canelas, R. Póvoa, N. Horta, and G. Dundar, "Using polynomial regression and artificial neural networks for reusable analog IC sizing," in: *Proc. IEEE Symp. Microelectron. Circuits Devices (SMACD)*, Lausanne, Switzerland (2019) 13–16. https://doi.org/10.1109/SMACD.2019.8795282

- [20] L.Y. Tseng and S. Yang, "Genetic algorithms for clustering, feature selection and classification," in: *Proc. IEEE Int. Conf. Neural Netw.* (1997) 1612–1616.

- [21] J. Bala, J. Huary, H. Vafaie, K. De Jong, and H. Wechsler, "Hybrid learning using genetic algorithms and decision trees for pattern classification," in: *Proc. IJCAI Conf.*, Montreal, Canada, Aug. 1995.

- [22] J. Kennedy and R. Eberhart, "Particle Swarm Optimization," in: *Proc. IEEE Int. Conf. Neural Netw.*, Perth, Australia (1995) 1942–1948.

- [23] J.-P. Hong and S.-G. Lee, "Low phase noise Gm-boosted differential gate-to-source feedback Colpitts CMOS VCO," *IEEE J. Solid State Circ.* 44 (2009) 3079–3091. [https://doi.org/10.1109/jssc.2009.203

- [24] C. Juang, Y. Chang, and J. Liu, "A Hybrid of Genetic Algorithm and Particle Swarm Optimization for Recurrent Network Design," *IEEE Trans. Syst., Man, Cybern.* 34 (2004) 997–1006.

- [25] A. Thakker Rajesh, R. Ranjan, and P. Kumar, "Automatic Design of Low Power Low Voltage Analog Circuits Using Particle Swarm Optimization with Re-Initialization," *J. Low Power Electron.* 5 (2009) 291–302.

- [26] V.K. Devabhaktuni, M.C.E. Yagoub, Y. Fang, J. Xu, and Q.J. Zhang, "Neural networks for microwave modeling: Model development issues and nonlinear modeling techniques," *Int. J. RF Microw. Comput.-Aided Eng.* 11 (2001) 4–21. https://doi.org/10.1002/1099-047X(200101)

- [27] T. Dhaene, J. Ureel, N. Fache, and D.D. Zutter, "Adaptive frequency sampling algorithm for fast and accurate S-parameter modeling of general planar structures," in: *Proc. IEEE MTT-S Int. Microw. Symp.*, Orlando, FL, USA (1995) 1427–1430. https://doi.org/10.1109/MWSYM.1995.406240

- [28] P.B.L. Meijer, "Fast and smooth highly nonlinear multidimensional table models for device modeling," *IEEE Trans. Circuits Syst.* 37 (1990) 335–346. https://doi.org/10.1109/31.52727

- [29] J. Mitchell and W. McDaniel, "Adaptive sampling technique," *IEEE Trans. Autom. Control* 14 (1969) 200–201. https://doi.org/10.1109/TAC.1969.1099144

- [30] U. Beyer and F. Śmieja, "Data exploration with reflective adaptive models," *Comput. Stat. Data Anal.* 22 (1996) 193–211. https://doi.org/10.1016/0167-9473(95)00048-8

- [31] V.K. Devabhaktuni and Q.J. Zhang, "Neural network training-driven adaptive sampling algorithm for microwave modeling," in: *Proc. Eur. Microw. Conf. (EUMA)*, Paris, France (2000) 1–4. https://doi.org/10.1109/EUMA.2000.338591

- [32] W. Qu, S. Singh, Y. Lee, Y.S. Son, G.H. Cho, "Design-oriented analysis for miller compensation and its application to multistage amplifier design," *IEEE J. Solid-State Circuits* 52 (2017) 517–527. https://doi.org/10.1109/JSSC.2016.2619677

- [33] D. Marano, A.D. Grasso, G. Palumbo, S. Pennisi, "Optimized active single-miller capacitor compensation with inner half-feedforward stage for

- very high-load three-stage OTAs," *IEEE Trans. Circuits Syst. I: Regular Papers* 63 (2016) 1349–1359. https://doi.org/10.1109/TCSI.2016.2573920

- [34] S.K. Rajput, B.K. Hemant, "Two-stage high gain low power OpAmp with current buffer compensation," in: *Proc. IEEE/GHTCE*, Shenzhen, China (2013) 121–124. https://doi.org/10.1109/GHTCE.2013.6-767255

- [35] S.M.H. Largani, S. Shahsavari, S. Biabanifard, A. Jalali, "A new frequency compensation technique for three stages OTA by differential feedback path: SMC, frequency compensation, differential feedback path," *Int. J. Numer. Model.: Electron. Netw.*, *Devices Fields* 28 (2015) 381–388. https://doi.org/10.1002/jnm.2013

- [36] S.M. Anisheh and C. Dadkhah, "A two-stage method for optimizing the parameters of CMOS operational amplifiers based on evolutionary algorithm," *CSI J. Comput. Sci. Eng.* 14 (2017) 1–10.

- [37] B.P. De, K.B. Maji, R. Kar, D. Mandal, and S.P. Ghoshal, "Application of improved PSO for optimal design of CMOS two-stage Op-amp using nulling resistor compensation circuit," in: *Proc. IEEE Int. Conf. Devices Integr. Circuits (DEVIC)*, Kalyani, India (2017) 110–115. https://doi.org/10.1109/DEVIC.2017.8073917

- [38] B.P. De, K.B. Maji, R. Kar, D. Mandal, and S.P. Ghoshal, "Design of optimal CMOS analog amplifier circuits using a hybrid evolutionary optimization technique," *J. Circuits Syst. Comput.* 27 (2017) 1850029. https://doi.org/10.1142/S0218126618500299

- [39] M.A.M. Majeed and P.S. Rao, "Optimal design of CMOS amplifier circuits using whale optimization algorithm," *Commun. Comput. Inf. Sci.* (2018) 590–605. https://doi.org/10.1007/978-981-13-2372-0\_53

- [40] H. Gupta and B. Ghosh, "Analog circuits design using ant colony optimization," *Int. J. Electron. Commun. Comput. Technol.* 2 (2012) 9–21.

- [41] S. Asaithambi, M. Rajappa, and L. Ravi, "Optimization and control of CMOS analog integrated circuits for cyber-physical systems using hybrid grey wolf optimization algorithm," *J. Intell. Fuzzy Syst.* 36 (2019) 4235–4245. https://doi.org/10.3233/jifs-169981

- [42] A. Ahmadihaji and A. Nabavi, "Design of a 30 GHz rotary traveling wave oscillator with improved frequency tuning range in 0.18 μm CMOS technology," *AEU Int. J. Electron. Commun.* 68 (2014) 1053–1057. https://doi.org/10.1016/j.aeue.2014.05.008

- [43] B. Jafari and S. Sheikhaei, "Low phase noise LC VCO with sinusoidal tail current shaping using cascode current source," *AEU Int. J. Electron. Commun.* 83 (2018) 114–122. https://doi.org/10.1016/j.aeue.2017.08.032 [44] I. Taha and M. Mirhassani, "A 24-GHz DCO with high amplitude stabilization and enhanced startup time for automotive radar," *IEEE Trans. Very Large Scale Integr. Syst.* 27 (2019) 2260–2271. https://doi.org/10.1109/TVLSI.2019.2924018

- [45] A. Karthigeyan, S. Radha, and E. Manikandan, "Single event transient mitigation techniques for a cross-coupled LC oscillator, including a single-event transient hardened CMOS LC-VCO circuit," *IET Circuits, Devices Syst.* 16 (2022) 178–188. https://doi.org/10.1049/cds2.12094

- [46] I. Ghorbel et al., "Design methodology of ultra-low-power LC-VCOs for IoT applications," *J. Circ. Syst. Comput.* 28 (2019) 950122. https://doi.org/10.1142/S0218126619501226

- [47] X. Sun et al., "A synthesizable constant tuning gain technique for wideband LC-VCO design," *IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst.* 39 (2018) 14–24. https://doi.org/10.1109/TCAD.2018.2878161 [48] F.J. Del Pino Suárez and S.L. Khemchandani, "A new current-shaping technique based on a feedback injection mechanism to reduce VCO phase noise," *Sensors* 21 (2021) 6583. https://doi.org/10.3390/s21196583